# Design and Implementation of MAC Protocol based CDMA system for solving Near Far Effect using VHDL

Aakanksha Devrari, Adesh Kumar, Shraddha Singh, Amit Kumar

Abstract — The paper focuses on implementation of MAC protocol system for solving near far effect in Ad-hoc networks. The main issue in Direct Sequence Code Division Multiple access (DS-CDMA) Ad-hoc network is the issue of a near-far problem. The near-far problem can severely affect packet reception, and consequently, network throughput. In the article, focus is done on utilization of both power and medium access control approaches. For the problem, a design based on DS-CDMA system is developed and channel access is governed with the help of MAC protocol. Modelsim10.2 (MXE) tool is used for functional and logic verification of each block. The Xilinx Synthesis Technology (XST) of Xilinx ISE 14.2i tool is used for synthesis of transmitter and receiver using Virtex 5 FPGA.

Index Terms— Direct Sequence Spread Spectrum (DSSS), Medium Access Control (MAC) protocol, Gold Sequence Generator, Very High Speed Integrated Circuit Hardware Description Language (VHDL).

# **1** INTRODUCTION

The world's 1st cellular networks were introduced in the early 1980s, utilizing analog radio transmission technologies like Advanced mobile phone System (AMPS) [1]. CDMA networks were first launched in 1995, and it provided roughly ten times more capacity than analog networks. Since then, DS CDMA has become the earlier growing of all wireless technologies, with over a hundred million subscribers worldwide.

In [5] authors proposed the direct sequence spread spectrum principle based code division multiple access (CDMA) transmitter and receiver is implemented in VHDL language for FPGA. In [7] author proposed the implementation of DS-CDMA transmitter using Verilog HDL. It explains the design for pseudo random Psuedo random Noise (PN) code and a direct sequence principle based wireless transmitter.

#### 2. DIRECT SEQUENCE SPREAD SPECTRUM

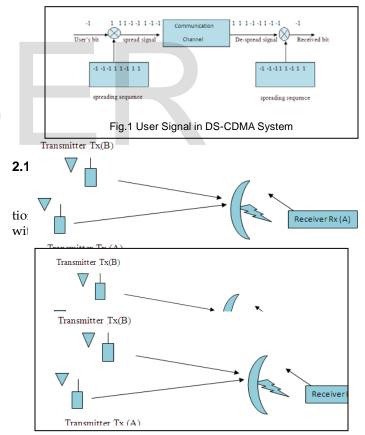

Direct Sequence is the best known spread spectrum technique. The data signal is multiplied by a PN code. A PN code is a sequence of chips valued -1 and 1 (polar) or 0 and 1 (nonpolar) and has a noise like properties, which results in low cross-correlation values among the codes and the difficulty to jam or detect a message. PN codes can be created by means of a linear feedback shift-register.

Author- M.Tech Scholar, UTU, Dehradun, India

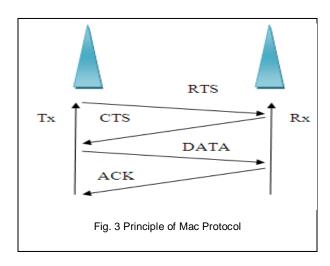

When all transmission powers are equal, and the receiver is much closer in distance to transmitter Tx(B) than Tx(A), the signal of Tx(B) will arrive at the receiver with a sufficiently larger power than that of the Tx(A), causing incorrect decoding of the transmission Tx(A).

Email- aks.uit08@gmail.com

<sup>1</sup>stCo-Author -Astt. Professor, (UPES, Dehradun, India

Email- adeshmanav@gmail.com

<sup>2&</sup>lt;sup>nd</sup> Co-Author -M. Tech Scholar, UTU, Dehradun, India

Email- aastha.singh238@gmail.com

<sup>3&</sup>lt;sup>rd</sup> Co-Author - M.Tech Šcholar, UTU, Dehradun, India Email- amit\_hardwar@yahoo.com

USER © 2014 http://www.ijser.org

#### **3 MAC PROTOCOL**

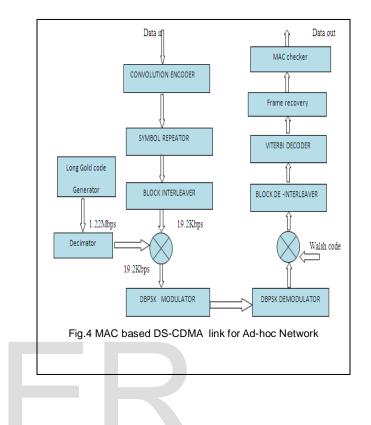

In the RTS/CTS algorithm, the node which wants to send frames sends a request to send (RTS) frame to the destination node first, and after the destination node responds with a clear to send (CTS) frame immediately. Only when the source node receives the CTS transmitted from destination node accurately; the source node is allowed to transmit frames. Whenever the source node receives the CTS, it starts the transmission of data. In order to face the unreliability of the channel, the MAC protocol adds a positive acknowledgement (ACK) upon the reception of a data packet. The proposed MAC based DS-CDMA solution provides a methodology in which after receiving the MAC ID from the transmitters, receiver firstly checks for the destination MAC in the received signal. If the ID matches with the self ID of the receiver it will allow the transmitter to send the data further. This will always restrict the non intended transmitter to transmit the data to the non intended receiver by providing the transmitter the information to reduce its power for transmission if the MAC ID comparison match fails .Principle of MAC is shown in the figure.3.

#### 3.1 Channel Access Mechanism

i) Step 1: If terminal 'j' has a packet to transmit, it sends a RTS packet at max. power value Pmax, and includes in this packet the maximum allowable power level (P(j)map) that terminal 'j' can use that will not disturb any ongoing reception in j's neighborhood. If the destination ID in RTS format matches with the self ID of receiver next step is to analyze power level.

• Request to Send (RTS) Frame: The frame structure for RTS signal is given below.

| No. of bits in RTS Frame-       |

|---------------------------------|

| Destination address/ID = 2 bits |

| Transmitter address/ID = 2 bits |

| Data Size = n bits              |

ii) Step 2: The intended receiver 'i' receives the RTS packet, and uses the pre-determined Pmax value and the power of the received signal P(ji) received to estimate the channel gain .

$$G_{fi} = \frac{P_{received}^{fi}}{P_{max}} \tag{1}$$

Terminal 'i' will be able to correctly decode the data packet if transmitted at a power P(ji)min given as-

$$P^{(ji)}_{min} = \mu^* (P_{thermal} + P_{MAI-current}^{(1)}) / G_{ji}$$

(2)

Where  $P_{thermal}$  = Thermal noise power ,  $P_{MAI \ current}$  = Effective current MAI from all already ongoing (interfering) transmissions,  $G_{ji}$  = Channel Gain . All neighbors of terminal 'i' will have to defer their transmissions during terminal i's ongoing reception.

iii) Step 3: Calculate the Power that terminal 'j' is allowed to use to send to 'i' is given as-

$$\mathbf{P^{j1}}_{allowed} = \xi_{max} \ \boldsymbol{\mu} * \mathbf{P_{thermal}} \ / \mathbf{G_{j1}}$$

(3)

Where  $\mu^*$  = Effective bit energy-to-noise spectral density ratio, Pthermal = Thermal noise power,  $\xi(\max)$  = Maximum planned noise rise.

If P (ji)allowed < P(ji)min, 'i' responds with a negative CTS to inform 'j' that 'i' cannot proceed with j's transmission

If P (ji)allowed > P(ji)min , 'i' calculates the interference power tolerance PMAI -future(i) that it can endure from future unintended transmitters .

$$P_{MAI \, future}{}^{(i)} = 3W \, G_{ji} \, (P^{(ji)}_{allowed} - P^{(ji)}_{min}) / 2 \, \mu^*$$

(4)

Where, W = Processing gain. 'i' equitably distributes this power tolerance among future potentially interfering users,  $\mu^* =$ Effective bit energy-to-noise spectral density ratio.

When responding to j's RTS, terminal 'i' indicates in its CTS the power level P  $^{(ji)}_{allowed}$  that 'j' must use. Also it inserts P (i) noise in the CTS packet and sends this packet back to terminal 'j' at maximum power.where, P  $^{(i)}_{noise}$  = Interference tolerance that each future neighbor can add to terminal 'i'.

• Clear to Send (CTS) Frame : The frame structure for CTS signal is given below

| ransmitter<br> dress/ID | Duration | Data Size | Allowable power  |        | Transmitter<br>Address/ID | Destination<br>Address/ID | Duration | Interference<br>Tolerance<br>Pi(noise) | Power<br>Pji (al-<br>lowed) |

|-------------------------|----------|-----------|------------------|--------|---------------------------|---------------------------|----------|----------------------------------------|-----------------------------|

|                         |          |           | Additional field | USER @ |                           |                           |          |                                        |                             |

No. of bits in CTS Frame-Destination address/ID = 2 bits Transmitter address/ID = 2 bits

iv) Step 4 : Compute  $P^{(s)}_{map}$ ; Potentially interfering terminal 's' hears the CTS message from 'i', then computes the channel gain Gsi between 's' and 'i' it also computes the maximum power  $P^{(s)}_{map}$  that s can use in its future transmissions.

$$\mathbf{P}^{(S)}_{\text{map}} = \min\left(\mathbf{P}^{(1)}_{\text{noise}}/\mathbf{G}_{\text{si}}\right) \tag{5}$$

v) Step 5: 'j' sends data to 'i'. If transmission is successful, receiver 'i' responds 'j' with an ACK packet over the data channel using the same power level that would have been used if 'i' were to send a data packet to 'j'.

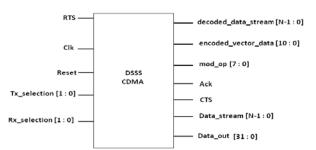

### 4 BLOCK DIAGRAM OF DS-CDMA MAC SYSTEM

Physical layer structure of MAC based DS-CDMA forward Link for Ad-hoc Network block diagram is shown in the Fig.4. The input data is represented by data which is a discrete N bit data. Convolution Encoder encodes redundant information into the transmitted signal, by improving the data capacity of the channel and making it immune to noise.

Next this encoded data stream acts as an input to Inter-leaver where shuffling (re-arrangement) of this data is done so as to remove burst errors in consecutive bits when data passes through channel.

In the next step Gold code sequence is generated using two pseudo noise sequences by means of a feedback shift register regulated by a timing clock. Decimator is used to reduce the data rate from 1.22Mbps to 19.2Kbps so as to make it compatible with the incoming data rate. Data bits then goes to DBPSK modulator.

Differential binary PSK is a non coherent form of phase shift keying which avoid the need for a coherent reference signal at the receiver. Walsh code is used which appears as arbitrary noise to a CDMA mobile terminal, unless that terminal makes the use of same code as the one which is used to encode the incoming signal. Next data goes to De inter leaver that rearranges the data in the proper sequence order.

In last step data bits is passed through Viterbi decoder that decodes de-interleaved data and results in the original sequence of data stream.

# **5 SIMULATION RESULTS**

The chip designing and synthesis is carried out in Xilinx 14.2 ISE software. The RTL view of the developed chip is shown in the figure 5 and the Modelsim simulation for the corresponding test vectors is shown in figure 6 and 7. Table 1 list the details supporting the RTL view and the Modelsim functionality. In the functional simulation, Reset is the input to reset, clk is used to provide a duty cycle and synchronize the transmitters and receivers. The transmitter and receivers are identified with their addresses, Tx\_selection is an input address of transmitters and Rx\_selection is an input address of receivers. Request to Send (RTS) is an input signal given the receiver to transmitter. Clear to Send (CTS) is the transmitter output to the receiver and ACK is the acknowledgment to the receiver from the transmitters. Data stream is of 'N' bits and encoded\_data\_vector length is of 11 bits depends on the encoding scheme.

The convolution encoder is used to encode the data. The decoded\_data\_stream is of 'N' bits which are decoded using Viterbi algorithm and actual data transfer form transmitters and receivers, which is of 32 bits which is data\_out [31:0]. The simulation is carried out with the assumption of four transmitter and four receivers. The transmitters have their addresses "00", "01", "10" and 11 sequentially. Similarly, receivers have their addresses "00", "01", "10" and 11 sequentially.

Fig.5 RTL view of DS-CDMA link for Ad-hoc Network

Fig.6 Simulation result for solving near far effect (MAC ID matches)

Fig.7 Simulation result for solving near far effect (MAC ID does not matches)

#### (n bits) system Clk Input to the DS-CDMA MAC used to provide positive (Rising edge) of clock (1 bit) Resets the data transmission states Reset (1 bit) Tx\_selection (2 bits) ID selection in RTS frame Self ID of receiver means receivers ad-Rx\_selection dress (2 bits) RTS Request to Send signal from Transmitter to Receiver CTS Clear to Send signal from Receiver to Transmitter ACK Acknowledgement on data reception Output of gold code sequence generator Data\_out Modulated gold code sequence with inter-Mod\_op leaved data Encoded\_vector\_data Encoded vector of convolution encoder (32 bits)

# TABLE 2 DEVICE UTILIZATION SUMMARY

| Logic Utilization          | Utilized | Available | Utilization |

|----------------------------|----------|-----------|-------------|

| Number of slices           | 492      | 6144      | 8%          |

| Number of slice flip flops | 779      | 12288     | 6%          |

| Number of 4 input LUTs     | 468      | 12288     | 3%          |

| Number of bonded IOBs      | 97       | 240       | 40%         |

| Number of GCLKs            | 3        | 32        | 9%          |

#### TABLE 1 DETAILS OF PIN

| Data_Stream Input to the DS-CDMA MAC protocol | Pin         | Description                       |

|-----------------------------------------------|-------------|-----------------------------------|

|                                               | Data_Stream | Input to the DS-CDMA MAC protocol |

# TABLE 3 TIMING PARAMETER SUMMARY

| Speed Grade | -12 |

|-------------|-----|

|             |     |

| 1.458ns   |

|-----------|

|           |

| 3.073ns   |

|           |

| 4.737ns   |

|           |

| 5.868 ns  |

|           |

| 202240 KB |

|           |

| 32        |

|           |

| 16        |

|           |

| Speed     |

|           |

| 1         |

|           |

| 100       |

|           |

It is also clear that MAC protocol governs the complete data transfer from transmitter to receiver. Each transmitter and receiver is allotted a MAC ID and data is transmitted only if the allotted MAC ID of both Tx i.e (00,01,10,11) and Rx (00,01,10,11) matches this enables the data transfer from the intended transmitter to intended receiver only and restricts the non-intended transmitters and their data remains in a temporary state i.e a garbage value.

Transmitter firstly sends a RTS to receiver, Receiver detects the ID of the transmitter and if this ID matches with the self ID of receiver then it sends with positive CTS to transmitter. Transmitter on getting a CTS frame sends data and if this data reaches the destination i.e to the receiver correctly receiver sends an acknowledge signal (ACK) confirming the data reception. Reset is the sequential input when reset = 1, the output = 0 and when reset = 0, the clock pulse signal is synchronized to provide actual output.

# CONCLUSION

In the paper a DS-CDMA MAC protocol system is designed and implemented on FPGA using VHDL language. From the simulation it is found that the hardware utilization in terms of no. of slices is 8%, no. of flip flops is 6 %, no. of bonded IOB's is 40%, no. of GCLKS is 9% and no. of 4 i/p LUTs is 3% which is extracted from the design. It is found that channel access mechanism approach adjusts the desired

# REFERENCES

[1] B.Sreedev, V.Vijaya, Ch.Kranthi Reeks, Rama Valupadasu and B.RamaRao Chunduri, "FPGA implementation of DSSS-CDMA Transmitter and receiver For ad-hoc networks" IEEE symposium on computer & Informatics, 2011, pp.255-260.

[2] B.S. Tripathi, Monika kapoor, "Review on DS-SS CDMA Tx and Rx for Adhoc Network" International Journal of Advances in Engineering & Technology, Vol. 5, Issue 2, Jan. 2013, pp. 274-279.

[3] D.D.Seth, Srikant Patnaik, Srikanta Pal, "A Quality of Service Assured & Faired MAC protocol for Mobile Ad-hoc Network", IEEE413, 2011, pp.413-417.

[4] Faisal Fayyaz Qureshi, "REECR-MAC: Reliable and Energy Efficient Cognitive Radio MAC Protocol for Ad-hoc networks" 2013 Fifth International Conference on Computational Intelligence, Modelling and Simulation, IEEE, 2013, pp.339-344.

[5] Hasan and J. G. Andrews, "The guard zone in wireless ad-hoc networks," IEEE Trans. Wireless Commun., vol. 6, March 2007, pp. 897–906

[6] Lu Ying, Kang Feng-ju, Zhong Lian - jiong, liang Xiang-yang, "Improvement Method of MAC Protocol Based on Ad-hoc Network Traffic Characteristic", IEEE, 2011, pp.464-467.

[7] M.Habib Ullah, Akhmad Unggul Priantoro, M.Jasim Uddin, ICCIT, "Design and Construction of Direct Sequence Spread Spectrum CDMA Transmitter and Receiver" Proceedings of 11th International Conference on Computer and Information Technology, 2008.

[8] Mihir Nyayate, Y.N Singh, "Dynamic Safe Transmit Power MAC protocol in Wireless Ad-hoc MAC Protocol". 2011 IEEE 179 TENCON 2011, pp.179-183.

[9] Muhammad Talha Zia, Faisal Fayyaz, Syed Sitwat Shah, "Energy Efficient Cognitive Radio MAC Protocols for Ad-hoc Network: A Survey". 2013 IEEE, pp.140-143. of Feedforward Classification Network Outputs, with Relationships to Statistical Pattern Recognition," *Neurocomputing – Algorithms, Architectures and Applications*, F. Fogelman-Soulie and J. Herault, eds., NATO ASI Series F68, Berlin: Springer-Verlag, pp. 227-236, 1989. (Book style with paper title and editor).

10] R. Sarojini, Ch.Rambabu, "Design and Construction of Direct Sequence Spread Spectrum CDMA Transmitter and Receiver". International Journal of Recent Technology and Engineering (IJRTE) ISSN: 2277-3878, Volume-1, Issue-3, August 2012, pp.169-174.

[11] S.-L. Wu, C.-Y. Lin, Y.C. Tseng, J.-P. Sheu, 2000 "A new multichannel MAC protocol with on-demand channel assignment for multi-hop mobile ad hoc networks", in: Proceedings of the International Symposium on Parallel Architectures, Algorithms and Networks, pp. 232–237.

[12] Sunil Kumar, Vineet S. Raghavan, Jing Deng, "Medium Access Control protocols for ad-hoc wireless networks: a survey". Elsevier B.V, 8 October 2004.

[13] S. Weber, J. G. Andrews, N. Jindal, "An overview of the transmission capacity of wireless networks," IEEE Trans. Communication, vol. 58, December 2010, pp. 3593–3604.

[14] Tasneem S. Mahbub, Salsabil. Ahmed, and Iqbalur R. Rokon "Transmitter Implementation Using DS-CDMA technique in FPGA Using Verilog ", International Conference on Electrical, Electronics and Civil Engineering (ICEECE'2011) Pattaya, Dec. 2011, pp.204-207.

[15] T.J Tsai & J.W Chen, "IEEE 802.11 MAC protocol over wireless mesh networks: problems and perspectives", in Proc. Advanced Information Networking and Applications, 19th International Conference, Volume 2, pp. 60-63.

# IJSER